# ClickNP: Highly Flexible and High Performance Network Processing with Reconfigurable Hardware

Microsoft<sup>®</sup> Research

Bojie Li<sup>§†</sup> Kun Tan<sup>†</sup> Layong (Larry) Luo<sup>‡</sup> Yanqing Peng<sup>•†</sup> Rengian Luo§† Yongqiang Xiong<sup>†</sup> Peng Cheng<sup>†</sup> Enhong Chen<sup>§</sup> Ningyi Xu<sup>†</sup> †Microsoft Research §USTC ‡Microsoft •SJTU

### Challenge: FPGA programming

Hardware description languages: Verilog, VHDL... Hard to program, hard to debug

## ClickNP: Making FPGA accessible to software developers

- Flexible: high-level language

- Modular: familiar Click abstractions

- High performance

- Joint CPU/FPGA packet processing

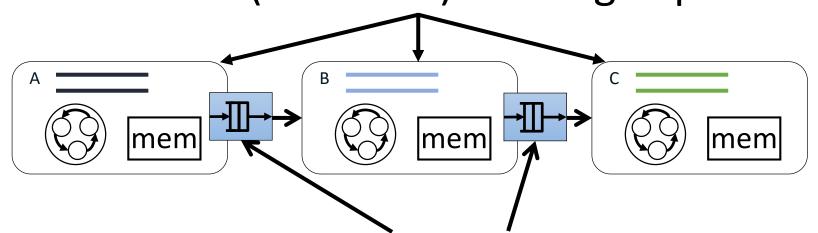

### **Programming model**

As if programming a multi-core processor cores (elements) running in parallel

communicate via channels, not shared memory

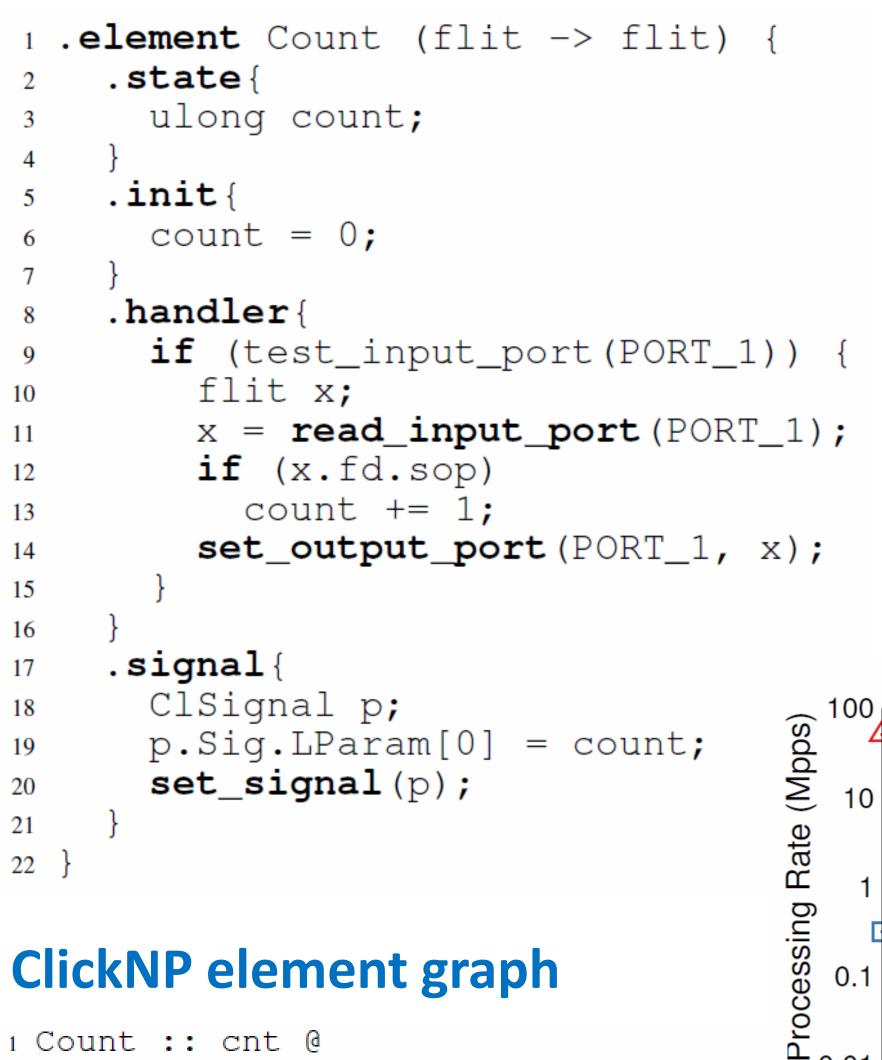

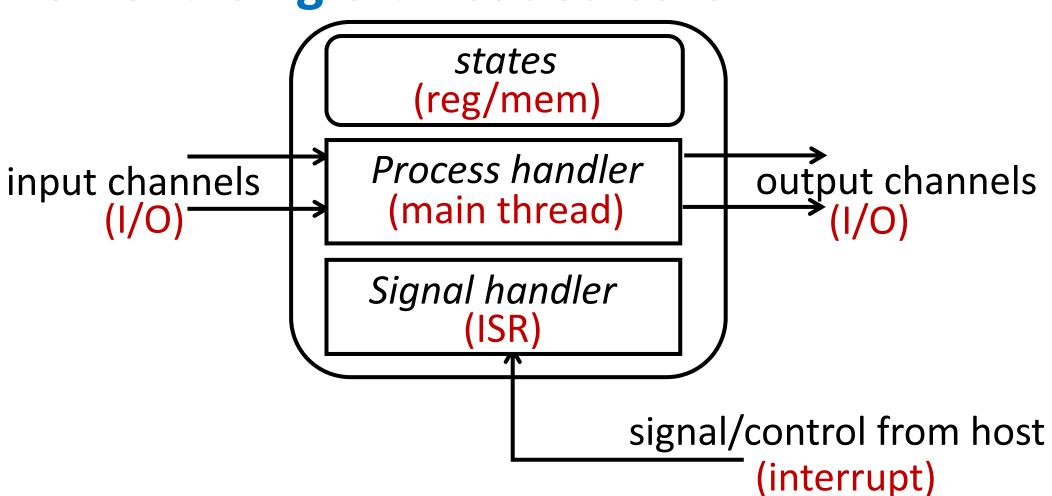

#### ClickNP element

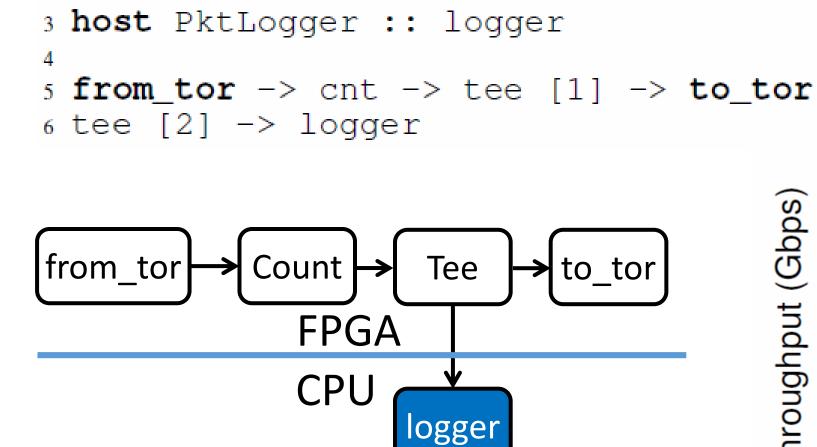

### ClickNP element graph

1 Count :: cnt @

2 Tee :: tee

#### Concurrent Flows 4 slots PCle -OpenCL 64M 1 slot PCle Throughput (Gbps) 10<sup>-3</sup> 10<sup>-4</sup> 1K 4K <sup>-</sup> Batch Size (Byte) 16K 64K 256 64

### **Element: single-threaded core**

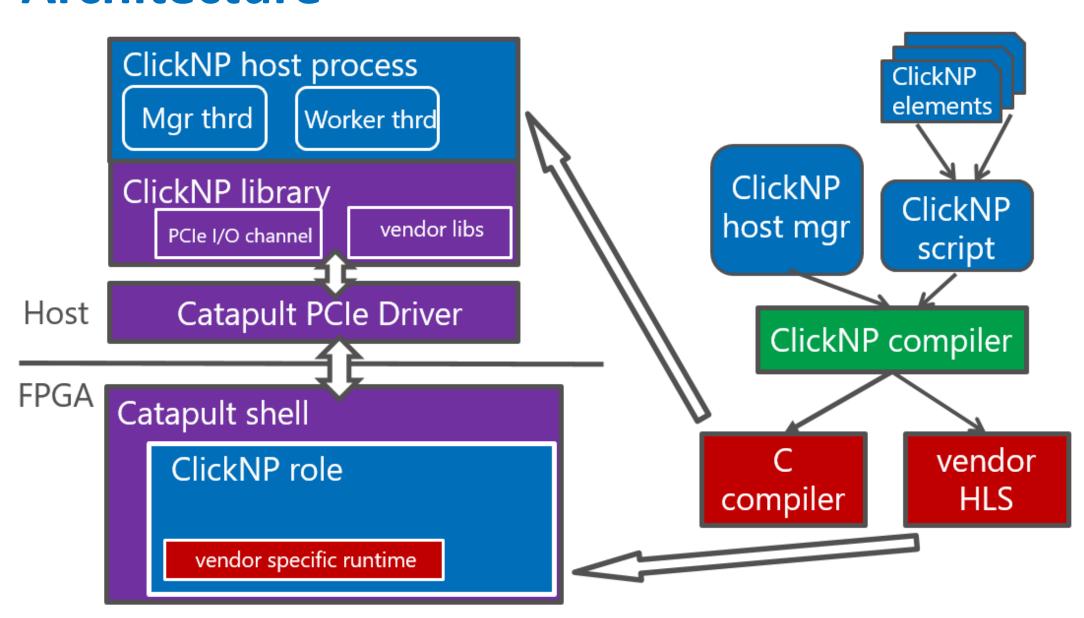

#### **Architecture**

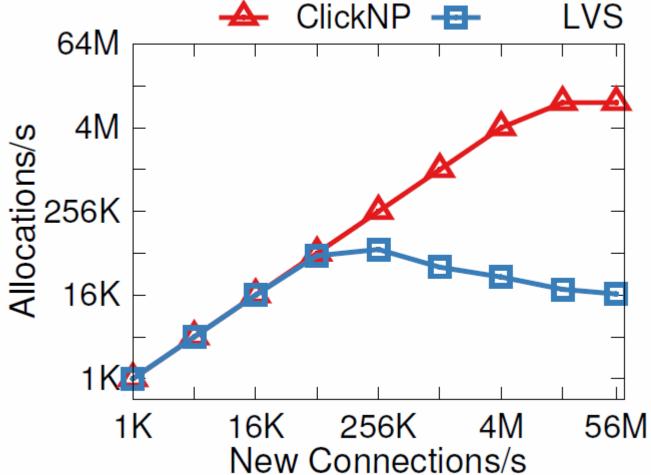

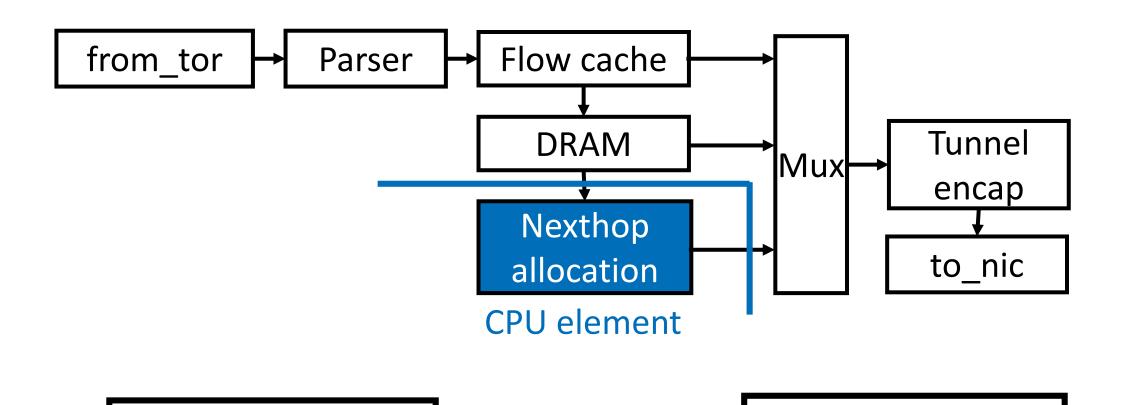

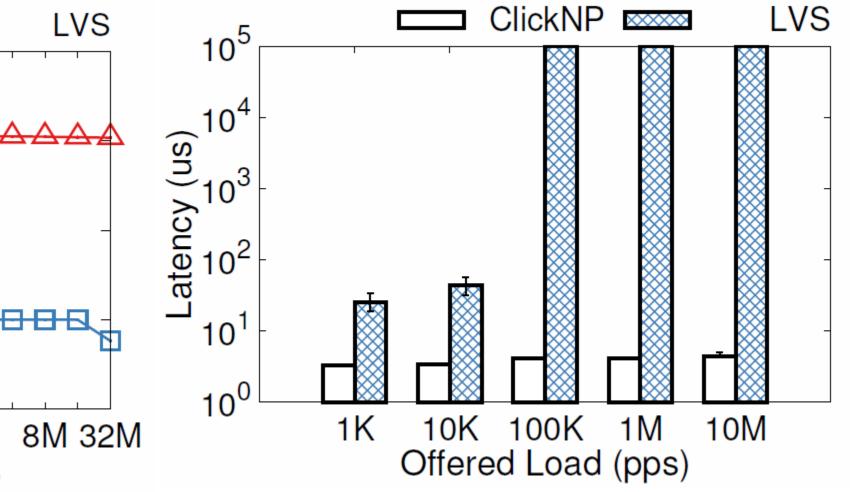

#### **Demo: Stateful L4 load balancer**

**FPGA**

TrafficGen

ClickNP -□

1K 4K 16K 128K

**FPGA**

Demo NF